About me

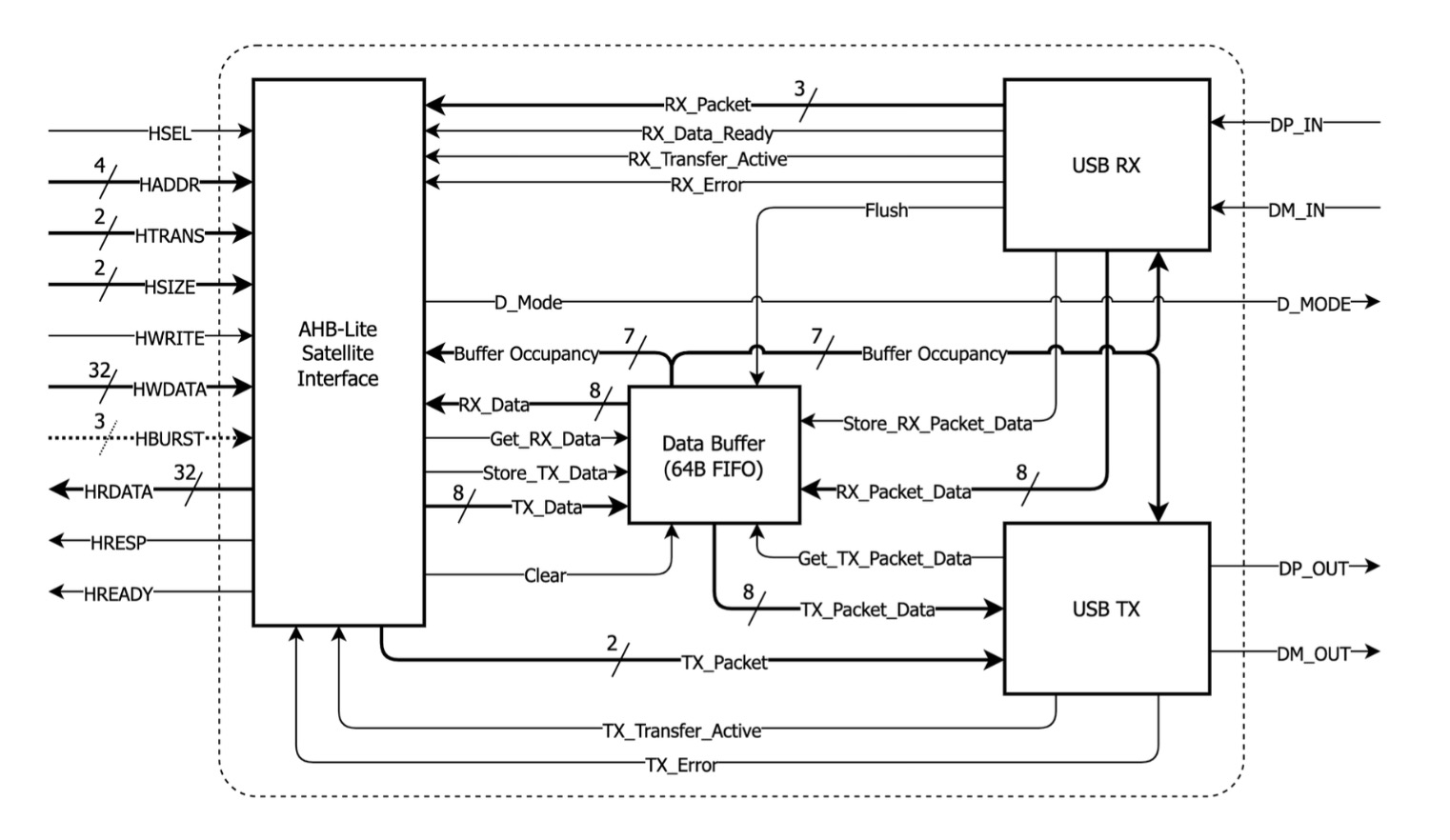

I’m a Computer Engineering student at Purdue University (graduating December 2025). My work spans ASIC and FPGA design, AI hardware accelerators, and fintech systems. I’ve designed RISC-V FPUs, USB SoC modules, and convolution controllers for tensor cores.

Professionally, I’ve been a Product Owner Intern at CIMB, collaborating with designers and developers on mobile banking features, I serve as a UTA for Python for Data Science, and I work for the Krenicki Center for Business Analytics and Machine Learning at Purdue as Undergraduate Student Researcher – Machine Learning and Predictive Models. My career goal is to build ultra-low latency hardware for financial trading systems.

Outside of engineering, I enjoy traveling, discovering new food, and exploring national parks.

View Resume