VIP 37921 JUNIOR PARTICIPATION FALL 2024

School of Electrical and Computer Engineering, Purdue University

SoCET – System on Chip Extension Technologies

# Floating Point Unit in RISC-V

# Fall 2024

Name:

Saandiya KPS Mohan

**Submission Date:**

11/27/2024

**Advisor:**

Dr. Mark C Johnson, Cole Nelson, Om P Kotwal

# **Summary:**

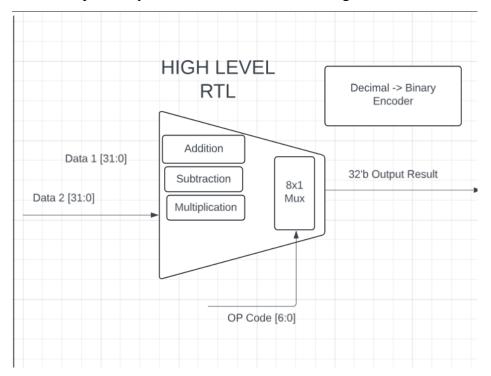

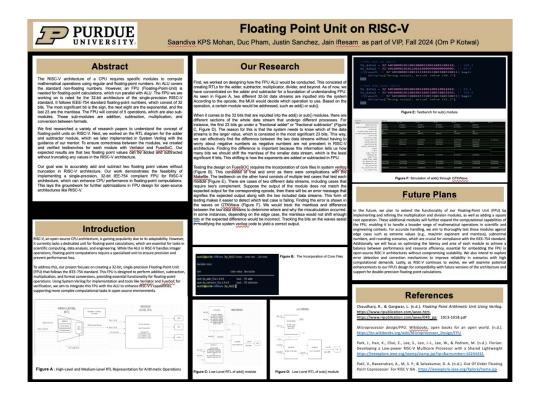

The project aimed to design and implement a 32-bit IEEE 754 compliant floating-point unit (FPU) as part of a RISC-V processor architecture. The primary focus was on creating modules for addition, subtraction, and multiplication that adhered to the IEEE standard. These modules required handling complex tasks such as normalization, alignment of operands, rounding, and addressing special cases like NaN, infinity, and subnormal numbers. The project achieved a significant milestone by completing the design and simulation of a functional FPU. I designed and implemented the floating-point adder and subtractor modules, ensuring proper handling of both common and edge cases. Through rigorous testbench creation and debugging, I verified their correctness under randomized and directed test scenarios. Furthermore, I collaborated with my team to integrate these modules into the larger FPU system and contributed to refining its overall performance and compatibility within the RISC-V architecture. The result was a robust and efficient FPU that met all design requirements and provided valuable insights into hardware design practices.

### Goals:

- Develop a deep understanding of IEEE 754 floating-point arithmetic.

- Designing the floating-point adder module, handling all IEEE 754 cases.

- Gaining hands-on experience with System Verilog for RTL design.

- Writing effective testbenches to verify module functionality.

- Collaborating with team members to ensure seamless integration of modules into the FPU.

- Make a poster explaining the background, device architecture, benchmarks, results, and future work in a poster and a presentation for the SoCET and Undergraduate Research Expo.

- Create a framework for future teams that want to work with FPU and add more cores to the system.

- Create weekly logs for future students to read and understand the design of the coherency unit.

- Provide documentation for future students on the FPU design on GitHub/SharePoint.

- Finish Professional Development activities, such as research ethics and working in a multicultural team, were selected specifically for this project.

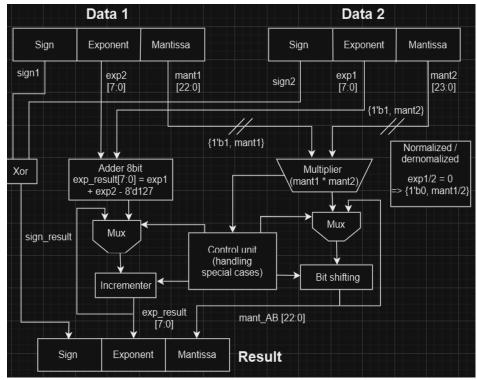

Initially, I planned to focus solely on the adder module. However, as the project progressed, I recognized the need to adapt to evolving team requirements. Midway through the semester, I expanded my responsibilities to include the multiplier module, which involved iterative design and debugging. Additionally, my goals shifted slightly to address challenges that arose during the project, such as refining the handling of subnormal numbers and optimizing the performance of the multiplier. Another change was the greater emphasis on debugging and integration. I took an active role in assisting team members with their modules, identifying and resolving compatibility issues during integration. These changes allowed me to broaden my skill set and contribute to the project's overall success more significantly.

## **Accomplishments and Learning:**

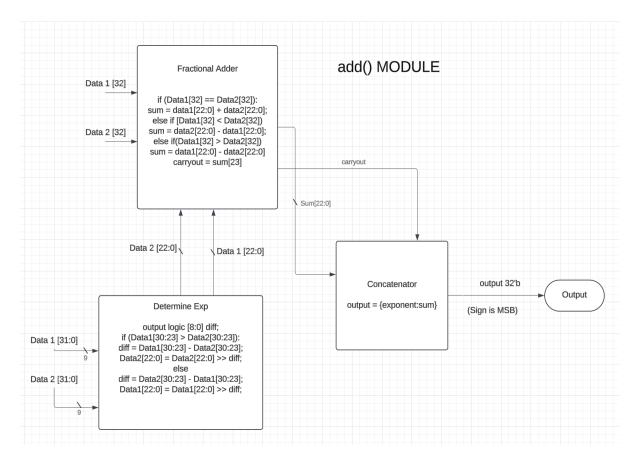

• Designed and implemented a 32-bit floating-point adder and subtractor module compliant with the IEEE 754 standard.

- Achieved proper operand alignment, normalization, and rounding. The module accurately handled special cases such as NaN, infinity, and subnormal values.

- Incorporated a robust normalization process using case statements for efficient shifting, ensuring the result adhered to the standard's precision requirements.

- Developed a comprehensive testbench to validate the module against directed and randomized test cases, ensuring accuracy under a wide range of conditions.

- Integrated the adder, subtractor and multiplier modules into the larger FPU system.

- Debugged module interactions and ensured compatibility between components.

- Contributed to finalizing the FPU's architecture by participating in team discussions and offering design optimizations to improve area and performance.

- Presented at the Undergraduate Research Expo and a SoCET meeting.

- Provided documentation for the Floating-Point Unit on GitHub/SharePoint for future designs.

- Finished all the PD Activities I planned for this project and learned a lot about ethics in research, intellectual property, working in a multicultural team, handling situations in these teams, and respecting everyone.

- Provided design logs weekly on the design of the floating-point unit, the research done for the project, and another discussion in the weekly meetings.

### **Teamwork:**

I worked with Justin Sanchez, Duc Pham Minh and Jain Iftesam on this project, and here are some of the contributions that they made:

- Justin Sanchez:

- Worked on testing the adder module with me.

- Worked on the final presentation at SoCET and the poster presentation we gave at the Undergraduate Research Expo.

- Worked on the abstract for the Undergraduate Research Expo.

- Presented the final presentation to the SoCET team, explaining the testing methods and IEE754 format.

- Duc Pham Minh:

- Designed an incomplete multiplication module.

- Worked on the slides for presentations, especially the multiplication slides.

Presented the final presentation to the SoCET team, explaining the multiplication modules.

#### • Jain Iftesam:

- Worked on the final presentation at SoCET and the poster presentation we gave at the Undergraduate Research Expo.

- Worked on the abstract for the Undergraduate Research Expo.

- Presented the final presentation to the SoCET team, explaining the background of FPU.

- Saandiya KPS Mohan:

- Designed the single precision adder, subtractor and top module for FPU, including the decoder.

- Tested and debugged adder and subtractor module.

- Provided documentation for the floating point unit and created the diagrams for the top-level system on GitHub for future designs.

- I finished all the PD Activities I planned for this project and learned a lot about ethics in research, intellectual property, working in a multicultural team, handling situations in these teams, and respecting everyone.

- Made a poster explaining the project's details, which I presented to multiple judges at the Undergraduate Research Expo.

- Worked on the final presentation at SoCET and the poster presentation we gave at the Undergraduate Research Expo.

- Worked on the abstract for the Undergraduate Research Expo.

- Presented the final presentation to the SoCET team, explaining the adder, subtractor, top module and future plans.

- Provided design logs weekly on the design of the coherency unit, the research done for the project, and another discussion in the weekly meetings.

### **Future Work:**

As I transition to my senior design project, I will not be continuing with the current FPU development. However, there are several potential directions for future work that others could pursue based on the progress made this semester. One area is optimizing the existing modules for improved performance and reduced area utilization. This could involve refining the multiplier logic or implementing more efficient normalization techniques. Additionally, future efforts could focus on extending the FPU's capabilities to include more complex operations, such as division and square root computation. These additions would enhance the processor's versatility and provide a more comprehensive arithmetic system. Another potential avenue is testing and integrating the FPU into a broader processor design, ensuring seamless compatibility and evaluating its performance in real-world applications. For someone continuing this project, documenting and debugging integration challenges, along with further developing verification environments for large-scale testing, would be invaluable.

# Appendix:

- <a href="https://purdue0-my.sharepoint.com/:p:/r/personal/sanch431\_purdue\_edu/Documents/Microsoft%20Team\_s%20Chat%20Files/FPU\_Presentation.pptx?d=w59a86129fac34b26bffe3391f8aaa2d3&csf=1&web=1&e=EGkOMa</a>

- Floating Point Unit in RISC-V.mp4

- <a href="https://purdue0.sharepoint.com/:o:/r/sites/ENGR-ECE-0-SOCET/">https://purdue0.sharepoint.com/:o:/r/sites/ENGR-ECE-0-SOCET/</a> layouts/15/Doc.aspx?sourcedoc=%7B9d92b34d-e064-4226-9957-cdfce583cf47%7D&action=editnew